... Да простит меня Gary!

В самом начале пути, силами самих разработчиков, была выложена некоторая информация по внутренней начинке CDD ConceRt. С тех пор коллекция практически не пополнялась, схемотехника и интерфейсы этого головного устройства URAL по сей день остаются тайной за семью печатями. По крайней мере, к MegaBus так и не был пристыкован каким-либо образом flash-носитель, кроме потенциальной перспективы подключения CompactFlash к ATAPI-box через переходник (?).

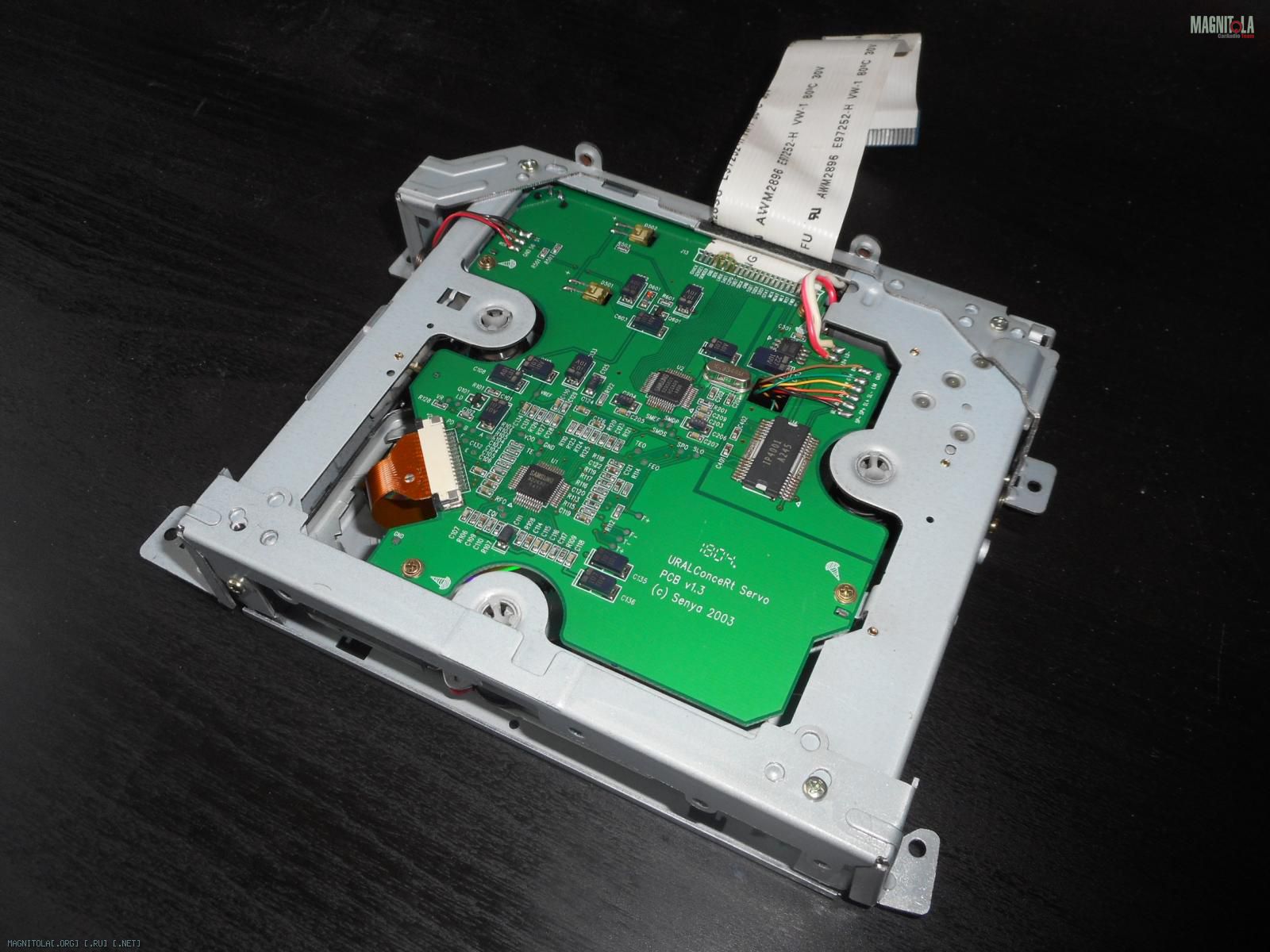

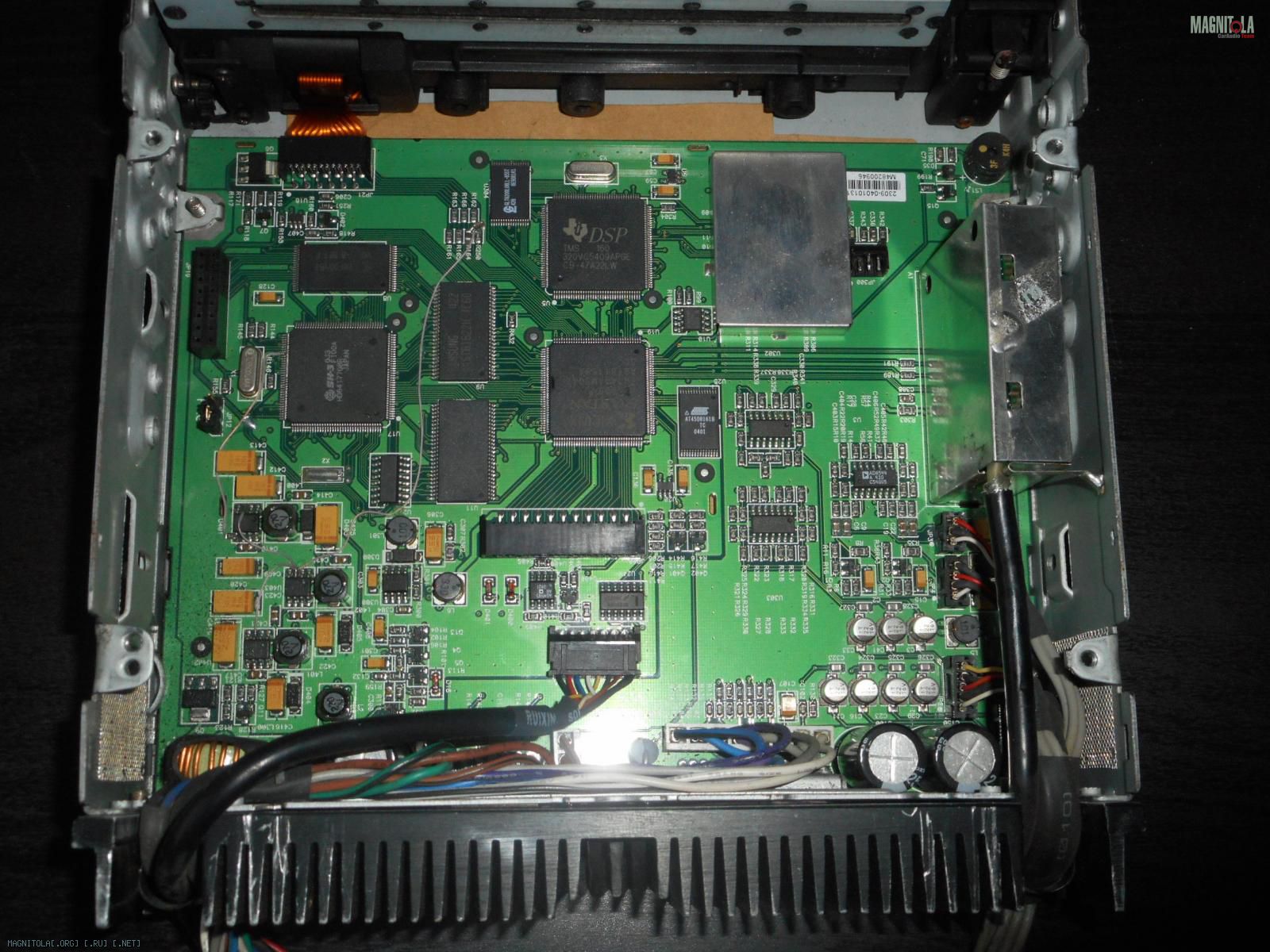

После снятия крышки корпуса, устройство легко разделяется на CD-транспорт с сервоплатой, и материнскую плату автомобильного компьютера:

На материнской плате не составит труда обнаружить RISC-процессор Renesas Electronics (Hitachi) SH3, ПЛИС Spartan (аналогично тому, что можно увидеть на подробных фотографиях ATAPI-box, а следовательно отвечающий каким-то образом за реализацию MegaBus в устройстве), несколько микросхем оперативной памяти и DSP Texas Instruments TMS320CV5409APGE.

Все кабели, включая линейные выходы, подключены через разъемы, включая незадействованный с +5V, на который удобно подпаивать стороннюю периферию:

Тем не менее, наиболее интересным в качестве отправной точки для апгрейда оказался разъем подключения CD-транспорта, причем на шелкографии уже подписаны все его линии:

Прослушивание осциллографом в режиме проигрывания MP3-диска показало следующую активность на них:

CHUCK - 0V

SENSE1 - +3V постоянные

SENSE0 - +3V постоянные

GND - 0V

BCK - 2.116 / 4.23381 Mhz 3.3v = BitClock аудиоинтерфейса

LRCK - 44.100 / 88.200 kHz 3.3v = WordClock аудиоинтерфейса

SADT - 3.3v = файловые данные, либо данные аудиоинтерфейса // UPD: 2015-10-17

C2PO - пачки коротких импульсов 3.3v

SBDT - 0V

SBCK - +3.3V постоянные

GND - 0V

SQDT - меандр с тактирующими импульсными вставками 3.3v

SQCK - подтянута к 3.3v, тактирующие импульсные сигналы, прижатые к 0

(SQCK vs. SQDT) =>

SDS1 - импульсы 3.3v

STAT - подтянут к 3.3v, пачки тактирующих импульсов, иногда прижимается к 0

MCK - подтянута к 3.3v, тактирующие импульсы с битовыми вставками

MDAT - инвертированные такты MCK

MLT - подтянута к 3.3v, периодические импульсы

RST - +3.3v постоянные

FWD - 0V постоянные

REW - 0V постоянные

+5V (не подписано)

0V (не подписано)

Из вышеперечисленного пока только очевидно есть основания предполагать, что, возможно, аудиоданные передаются в декодированном виде на материнскую плату в формате I2S, и, следовательно, могут быть легко смодулированы сторонним микроконтроллером Тем не менее, один из разработчиков заверил, что по этой линии передаются файловые данные для последующего декодирования средствами операционной системы.

Для построения эмулятора CD-привода, к которому может быть подключен иной внешний носитель, также необходимо, как минимум, уметь перехватывать и моделировать управляющие последовательности.

Полезные темы:

Форум автозвука и установки музыки в автомобиль

Социальные закладки